性能逆天的这种电容,你见过吗?

发布时间:2022-12-12 17:07

作者:一博科技高速先生成员 孙小兵

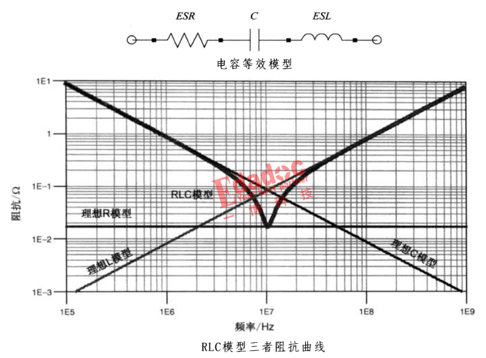

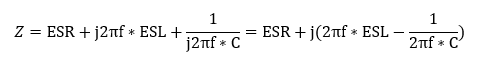

我们都知道,理想状态下电容的阻抗是随频率的增加而逐渐减小的。但在实际运用中,由于电容器存在等效电感(ESL)以及在电路板上存在一定的安装电感,当频率上升到一个特定值后电容的阻抗将不再减小,反而是逐渐增加的趋势变化。这个特定频率就是电容的自谐振频率。在谐振频率之前,电容器呈现容性特征,在谐振频率之后,电容器将呈现感性特征。

实际电容的特性阻抗表示公式为:

寄生电感存在,影响了电容器在高频段的滤波特性。而三端子电容可以通过其独特的结构优势从而改善寄生电感的影响,从而使得电容器在高频段的滤波特性得到改善。

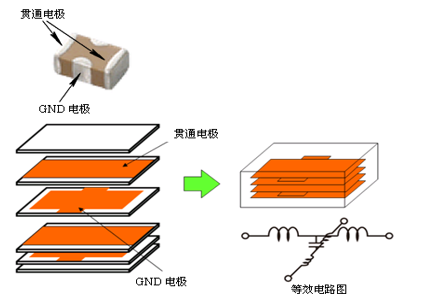

三端子片状多层陶瓷电容器的结构如下图所示。在电容器的两头为贯通电极,两边接地,每层中间为电介质,贯通电极与接地电极交互层叠,从而形成类似于穿心电容器的结构。贯通电极的少量残留电感可以起到类似于T型滤波器的电感作用,因此可减小寄生电感的影响。此外,由于接地端连接距离较短,因此该部分的电感也非常微小。并且,由于接地端连接两端,因此呈并联连接状态,电感也将降低一半。

以下是三端子电容的原理图封装和C0603型及C0402型封装。其中1、3引脚为贯通电极,可以作为电源端,2、4引脚为GND电极。

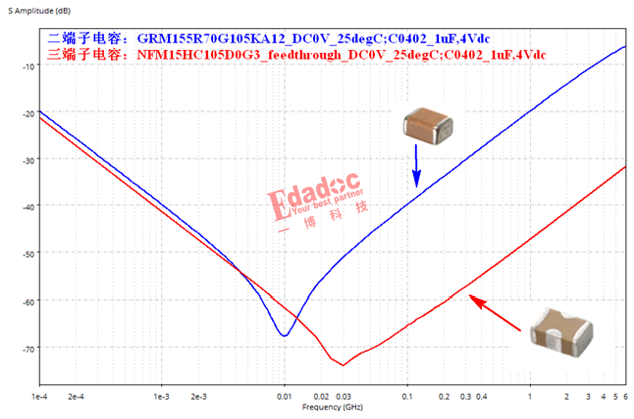

下图是普通二端子陶瓷电容和三端子陶瓷电容的插入损耗性能对比。单从两种电容自身的特性来看,它们的电容量相同,因此在低频范围内特性相同。但二端子电容器损耗最低点在10MHz频点附件,在频率超过10MHz后性能便开始下降。而三端子电容器在超过30MHz后才出现性能下降。故三端子电容器的高频特性更好,有效滤波的频带范围更宽泛,适用于需要去除高频噪声干扰的case。

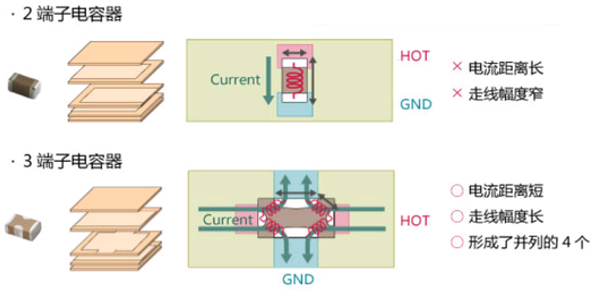

三端子电容优势一:低ESL。由于三端子电容存在两个贯通电极和两个地极,电流通过电容的距离较短,并且可以有4个电流滤波通路,这种结构使得三端子电容的ESL较低,自谐振频率点更高,且高频衰减特性更好。同时通过加粗、缩短高频电路路径可实现更低的ESL特性。

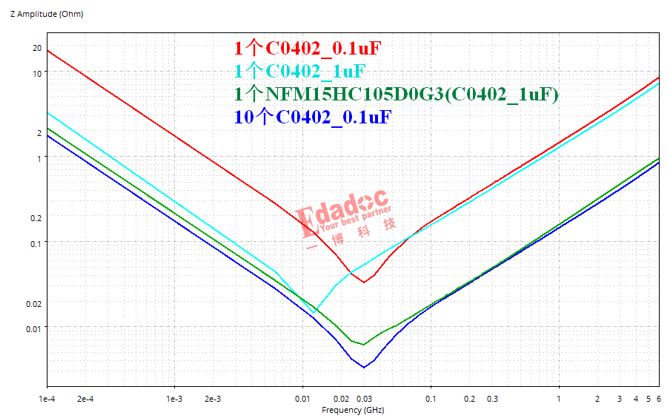

优势二:减少电容数量。使用低ESL电容器,可维持与二端子电容器相同功能。同时可以得到更好的高频特性。如下图几种电容特性阻抗图,红色是单个0.1uF普通电容的阻抗曲线,青色是单个1uF普通电容的阻抗曲线,绿色是单个1uF的三端子电容的阻抗曲线,蓝色是10个0.1uF的普通电容的阻抗曲线,可以看到单个1uF的三端子电容和10个0.1uF的普通电容在低频段和高频段的阻抗特性曲线是一样的。这说明使用三端子电容可以替换更多数量的二端子电容并达到相同的滤波效果。

这里也告诉大家一个好消息,村田已开发出了汽车用1005M(C0402)尺寸电容器中的4.3µF超大静电容量3端子多层陶瓷电容器“NFM15HC435D0E3”,并且已经开始量产。相信在不久的将来就能面向市场运用。