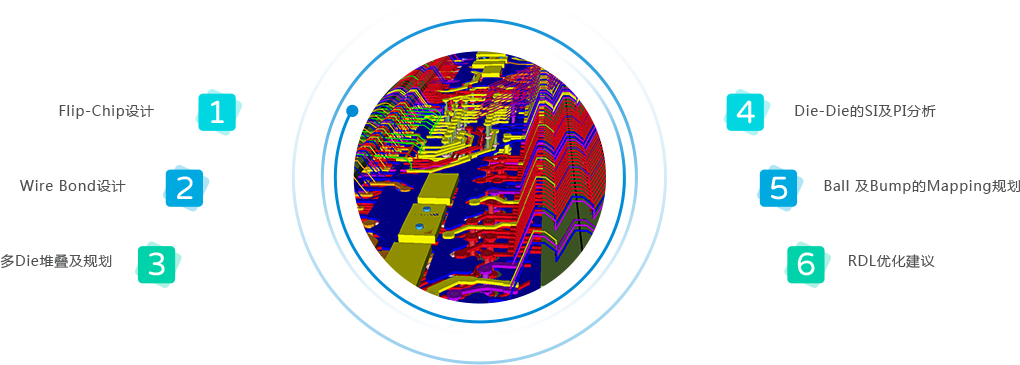

SiP设计能力

SiP设计优势

- 芯片-封装-系统协同规划与设计

- 仿真与设计同步进行

- Wire Bond 3D建模

- 仿真精度高,优化准确

- 熟悉主流的封装基板生产工艺

- Hspice模型转IBIS模型

- 可协助生成设计指导书

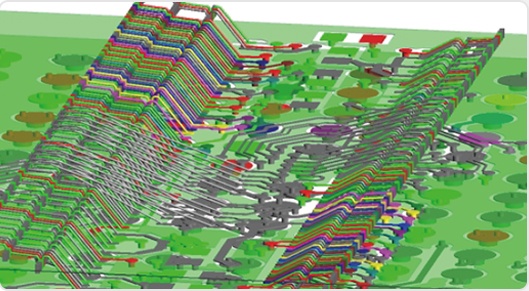

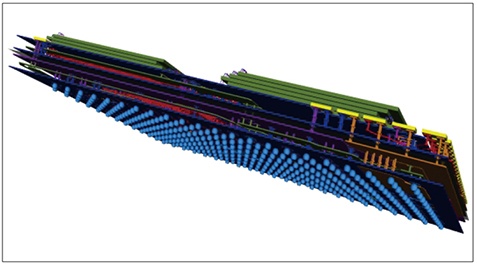

SiP设计案例展示

- 9个DDR4颗粒,4+5层堆叠

- DDR4运行速率3200Mbps

- 整体性能媲美SO-DIMM

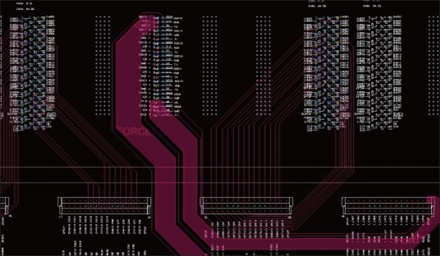

ATE能力介绍

- 待测试芯片pin数多,多达几千pin

- 叠层多达40层以上, 板厚超过5mm

- 走线和过孔的设计和加工趋于极限能力

- 需要进行精确仿真来保证走线不会影响芯片测试精度