瞧不起谁啊!“缝合电容”我怎么可能不知道

发布时间:2025-04-28 17:39:55

高速先生成员-- 黄刚

作为三大分立元器件之一的电容,的确身上挂满了title,之前的高速先生文章中也部分描述过它的用途,例如用作电源网络的去耦电容和用作高速串行链路中的隔直电容。今儿我们再普及它的另外一个作用---缝合!

本着高速先生的一贯风格,主打一个不讲道理,额,不是!是不讲太多深奥的理论,希望以直观形象的仿真结果来说明问题。所以一上来我们就直奔仿真建模,通过仿真让大家轻松“get”到要点。

案例1:

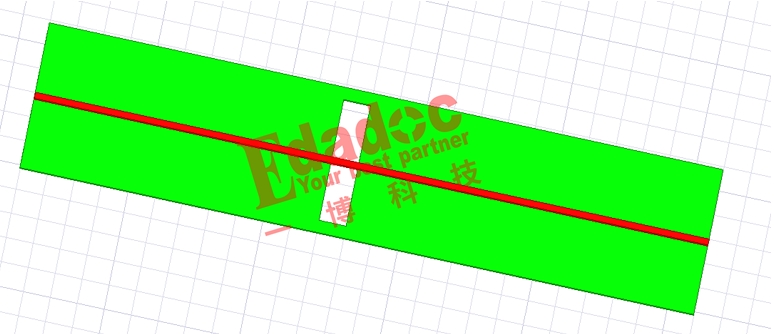

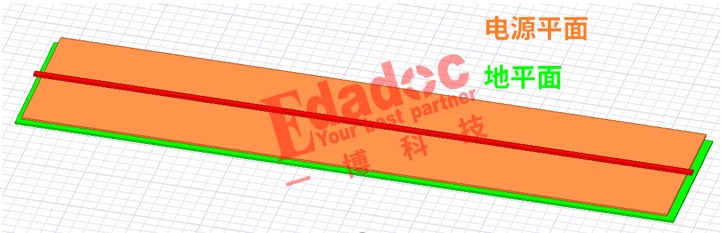

相信很多人都遇到走线跨分割地平面的情况,例如下面的模型所展示的:

大家都知道跨分割肯定对信号有影响了,那你们能想到的优化方案是什么呢!什么,告诉我不跨分割平面不就解决了吗!要是能不跨分割平面,鬼都知道肯定是最好的解决方案啦!那如果在避免不了跨分割的情况下呢?相信部分资深的硬件工程师或者设计工程师就会条件反射的想到这样去做,那就是在地平面跨分割的位置整上1到2个电容。

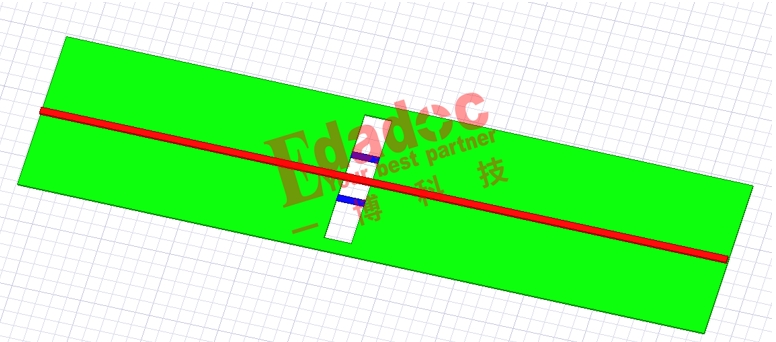

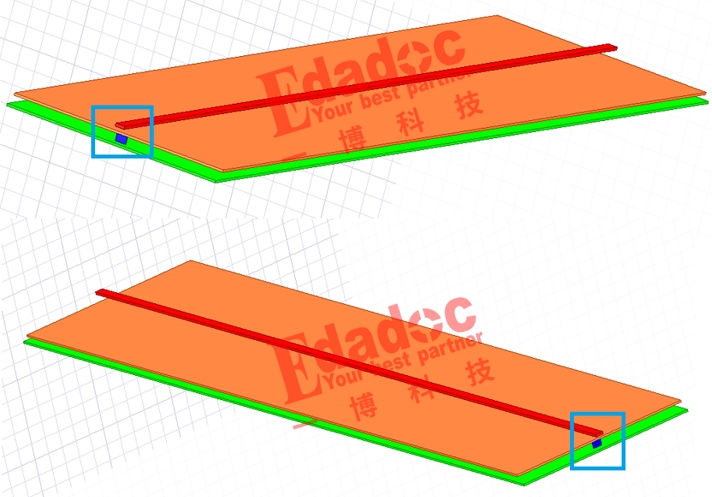

具体怎么放?就像下面蓝色器件这样放。

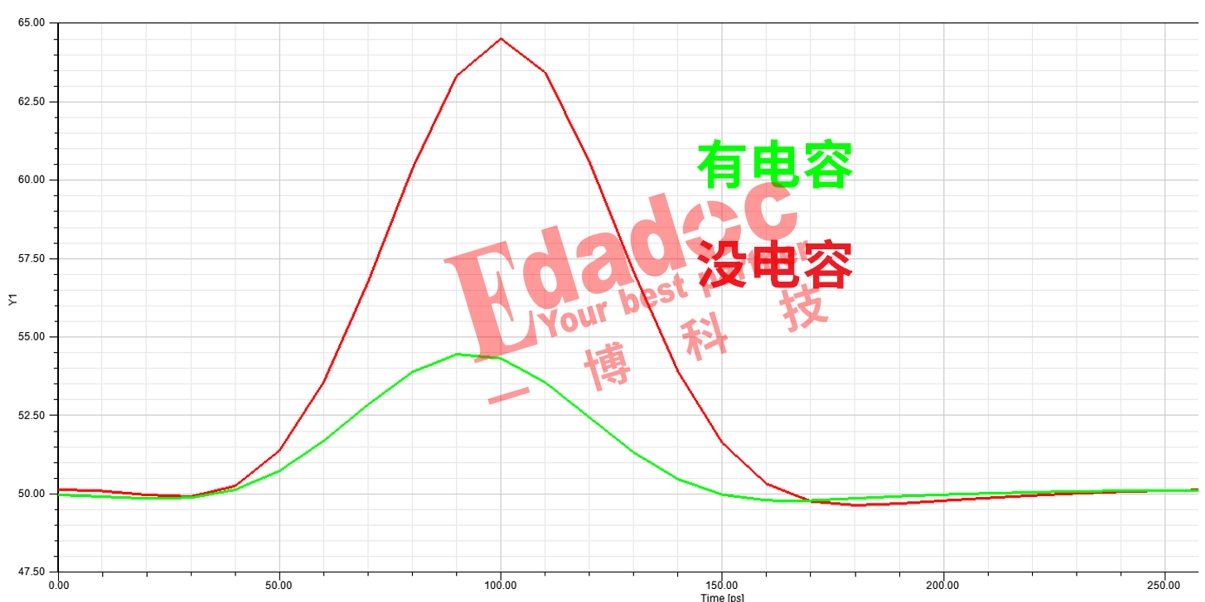

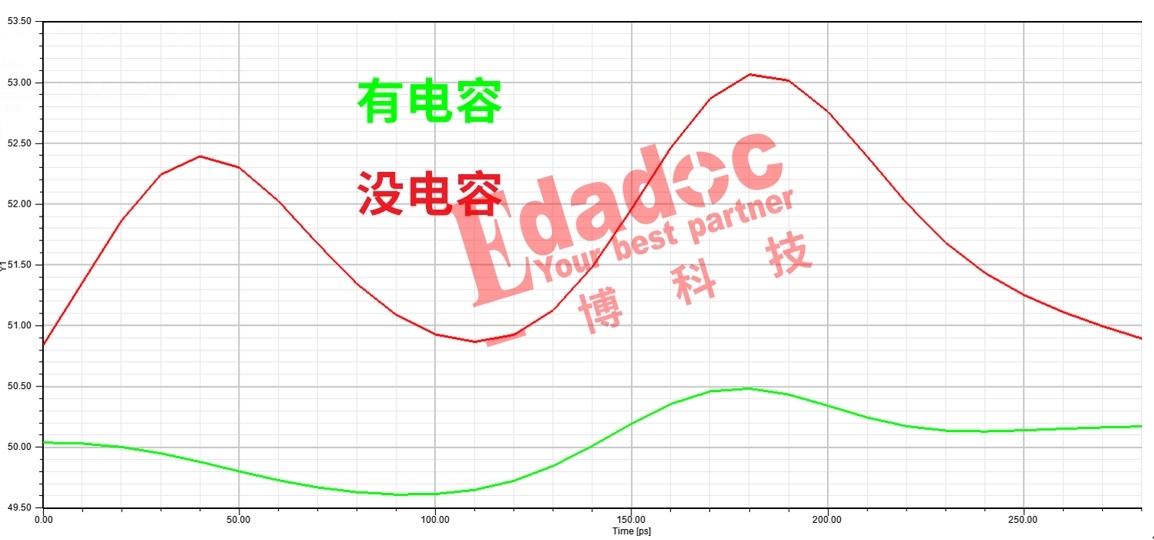

从仿真结果上看,放和不放电容的插损对比是这样的。。。

而在跨分割位置的TDR阻抗结果对比是这样的:

案例2:

线还是那根信号线,我们换个场景,让这根信号线只能参考电源平面,没法直接参考地平面,如下所示:红色信号线参考的是下面层的橙色电源平面,电源平面再下一层才是本来需要参考的地平面。

当然,高速先生从来也没说过信号线就不能参考电源平面了。你如果硬要直接按上面的模型去做设计的话,也不是说一定会挂!这时候,还是案例1那帮资深工程师又有解决方案了,那就是下面的样子!

在走线首尾两端的电源平面和地平面之间各加一个电容,如下面蓝色东东所示。

还别说,资深就是资深,加了电容后,信号质量就是比你直接不加电容硬做的来得好。

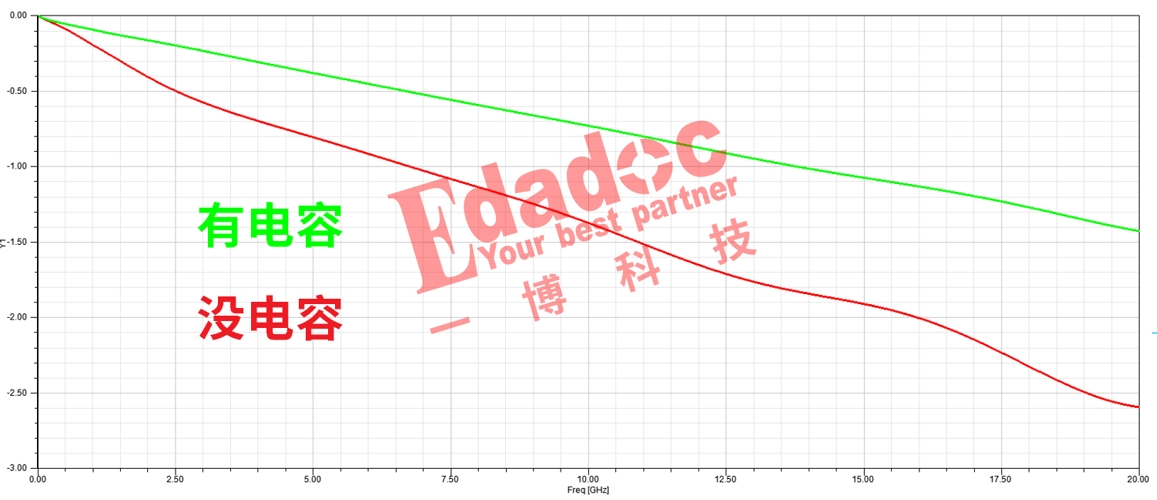

插损对比结果如下:

TDR阻抗结果对比如下:

案例3?由于篇幅已经很长了,就当没有了吧!当然本身缝合电容能用到的设计场景肯定是有很多的,在一些非常规的设计中,用上它之后的改善度可以非常的大。快到假期了,相信大家也不太想看那么多字了哈,留下后面的一个思考问题,就这样了哈!