PCB加工中的“流胶”到底是怎么影响阻抗的?

发布时间:2025-12-08 08:43:08

高速先生成员-- 黄刚

高速先生成员-- 黄刚随着产品速率越来越高,人们对传输线阻抗偏差的接受度也肯定越来越小了,大家都怀揣着加工出来的板子传输线阻抗能做到10%、8%甚至5%误差的梦想。有梦想绝对是好事,高速先生支持每一个有梦想的人。但是光有梦想肯定控不好阻抗,高速先生一定会把你们摇醒,让你们好好思考下到底有什么因素会影响加工的阻抗误差哈!

影响阻抗的因素有很多,高速先生之前文章也写过不少,今儿再给大家分享一些影响指数也贼高的因素,那就是流胶。。。

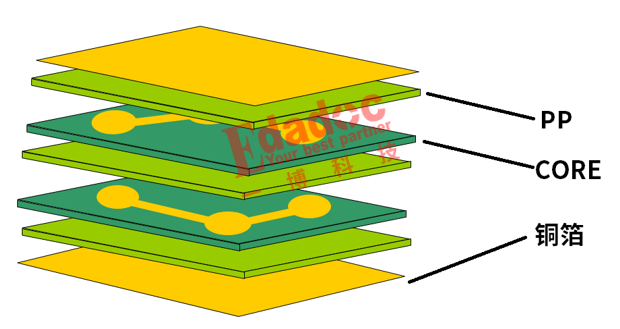

什么是流胶?的确又要花点篇幅从PCB加工工艺说起了。首先PCB叠层的组成大家应该知道哈。无论是多少层PCB板(当然2层除外哈),它的组成部分都会由以下三个元素组成,那就是PP,CORE和铜箔。

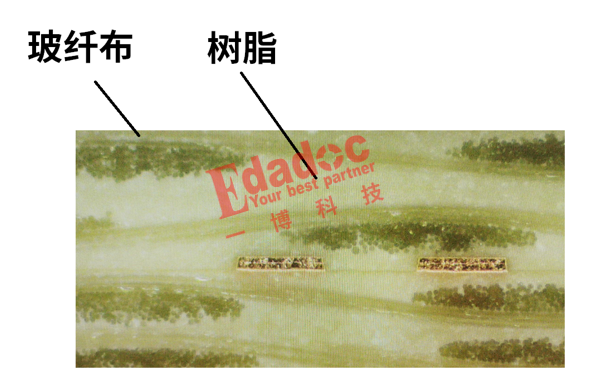

铜箔大家好理解,那就是铜嘛。PP和CORE大家都也不用觉得他们差异很大,先说下PP哈。我们叫习惯了PP,其实它的学名叫半固化片Prepreg,它的组成元素就2个,玻璃纤维布和树脂,就像下面的切片图所示。

真实长啥样?就是下面那样了。其中玻璃纤维布,简称玻纤布,树脂,俗称胶水,它就是我们今天的要说的流胶的那个胶了哈!

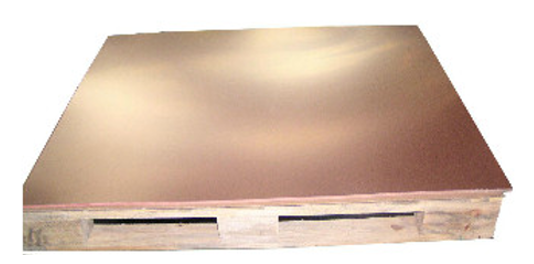

那什么叫CORE呢?也没什么复杂,那就是把PP上下各加上一张铜箔,预先压合一次,本质上就是一个双面板,所以CORE的学名也叫芯板,就是下面那样了。

CORE和PP的差异点主要是2个,一是CORE多了上下两面的铜箔,二是CORE是预先压合好的PP,把CORE和PP在多层板中叠好再次高温压合的时候,CORE是不会再变化的了。那怎么能把多张CORE和PP压合成一个稳定的多层板呢?就主要靠CORE上下的PP里面的胶了。压合时的高温会把PP里的胶变成近似液体状,然后填充多层板里面的空隙,最后像胶水一样把多个CORE粘起来。

那流胶就是把多个CORE粘起来嘛,为什么会影响传输线的加工偏差呢?最近刚好有一个客户的阻抗测试结果,我们一起拿出来看看大家就知道了。

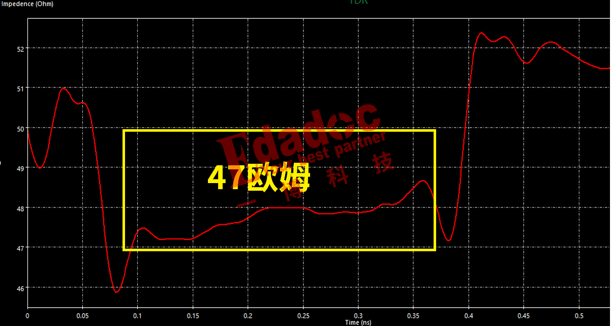

高速先生的一贯风格,先说结论,那就是测试发现50欧姆传输线的阻抗加工后偏低了,只做到了47欧姆左右。因为这个是客户的一块要求非常高的测试板,因此47欧姆就不很好了。

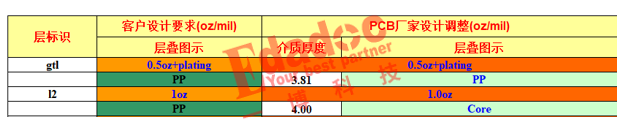

那要分析原因,首先就看看叠层?这个信号线走L2层,参考L1和L3层,L2和L3就是一个CORE了,L1层就是单独的铜箔,L1和L2之间是PP。

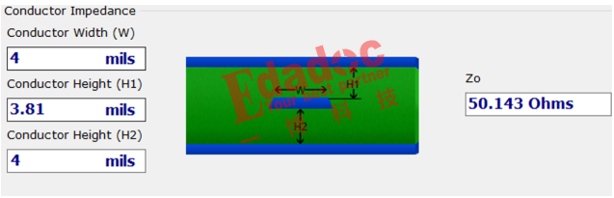

根据工厂确认的叠层厚度和线宽,我们算了下阻抗,算出来是很好的,妥妥的50欧姆!

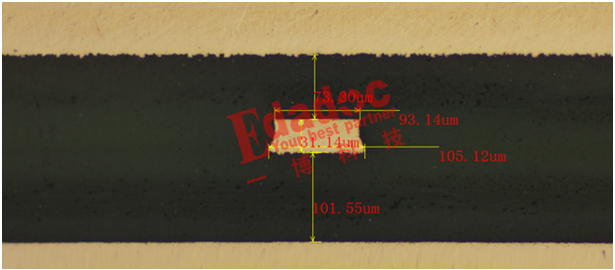

那肯定是加工时哪个因素变掉了导致阻抗偏低呗。客户很纠结,一定要找到原因,那没办法了,板子数据测试后,我们只能拿去切片看看了。不看不知道,一看吓0.5跳。

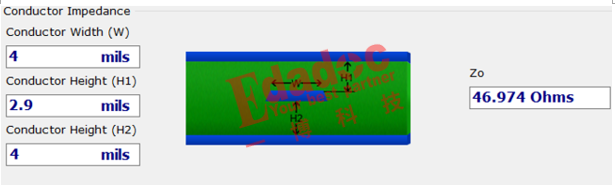

能看到线宽和设计的4mil基本上出入不大,下面L2和L3层的CORE也很稳定,在4mil左右。最大的问题是L1和L2层的PP厚度咋就和确认的叠层差那么远呢?叠层上明明写的厚度是3.81mil,切片看到的只有2.9mil,少了1mil那么多?!和板厂确认了PP的型号是对的,用的PP本身的厚度就是3.8mil左右没毛病。3.8mil的PP压合完只有2.9mil了?

的确,最大的问题就是在这里,如果L1和L2层的PP厚度从3.8mil变成2.9mil后,加工出来的阻抗就真的变成了47欧姆左右了,也。。。没毛病!!!

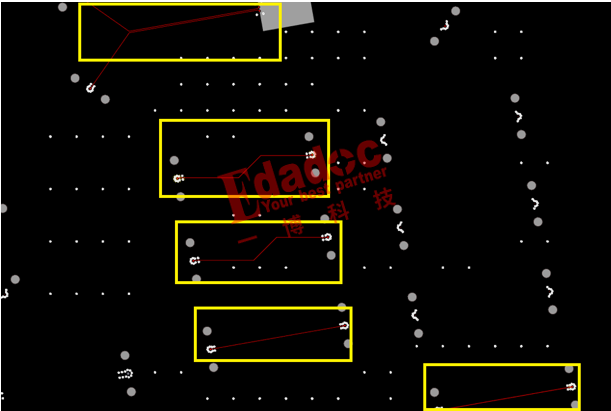

对啥啊对,47欧姆阻抗我会算啊,关键是为什么PP压合后直接少了将近1mil啊,我想知道的是这个问题啊!!由于这个项目是客户自己画的测试板,那我们就提出要不看看客户的设计图。打开设计图看到之后,客户率先发表意见:你们看,在L2层为了排除其他走线的干扰,我就只走了7、8根待测的信号线,其他都是空的啊,应该不存在走线之间的干扰导致阻抗变化啊!的确啊,这一层也就那么几根信号线,都离得远远的,肯定不会有什么干扰啊!

终于到高速先生发话了:这就对了嘛!

简单的几个字就定位了阻抗偏低的最大问题。。。